## ACPL-355JC

# 10A IGBT and SiC MOSFET Gate Drive **Optocoupler with Integrated Overcurrent** Sensing, FAULT, and UVLO Status Feedback

#### Description

The Broadcom® ACPL-355JC is a 10A intelligent gate drive optocoupler. The high peak output current and wide operating voltage range make it ideal for driving IGBT or SiC MOSFET directly in motor control and inverter applications.

The device features fast propagation delay with excellent timing skew performance. It provides IGBT/SiC MOSFET with overcurrent protection and functional safety reporting. This full-featured and easy-to-implement gate drive optocoupler comes in a compact, surface-mountable SO-16 600V CTI package. It provides reinforced insulation certified for safety regulatory IEC/EN/DIN, UL, and cUL.

#### **Features**

- 10A maximum peak output current

- 140-ns maximum propagation delay

- Dual output drive to control turning on and off time

- Overcurrent detection with configurable "Soft" shutdown

- Functional safety reporting

- Overcurrent FAULT feedback

- UVLO status feedback

- Under voltage lockout (UVLO) with hysteresis

- 100-kV/µs minimum common mode rejection (CMR) at  $V_{CM} = 1500V$

- 15V to 30V wide operating V<sub>DD2</sub> range

- –40°C to 110°C industrial temperature range

- CTI > 600V with 8.3-mm creepage and clearance

- Regulatory approvals:

- UL/cUL 1577 5000 V<sub>RMS</sub> for 1 minute

- IEC 60747-5-5  $V_{IORM}$  = 2262  $V_{PEAK}$

## **Applications**

- Mid-voltage motor drives

- 1500V solar inverter and wind inverter

- Static var generator (SVG)/high voltage converter (HVC)

**CAUTION!** Take normal static precautions in handling and assembly of this component to prevent damage, degradation, or both that may be induced by ESD. The component featured in this data sheet is not to be used in military or aerospace applications or environments. The component is also not AEC-Q100 qualified and not recommended for automotive applications.

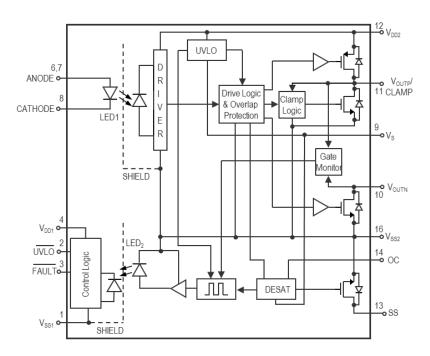

# **Functional Diagram**

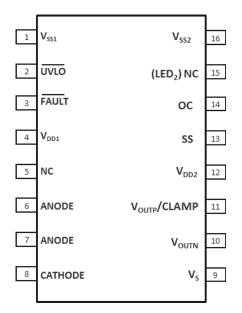

# **Pin Description**

| Pin | Symbol                   | Description                                                                                                                                                                           |

|-----|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>SS1</sub>         | Input ground                                                                                                                                                                          |

| 2   | UVLO                     | V <sub>DD2</sub> under voltage lockout feedback                                                                                                                                       |

| 3   | FAULT                    | Overcurrent fault feedback                                                                                                                                                            |

| 4   | $V_{DD1}$                | Input power supply                                                                                                                                                                    |

| 5   | NC                       | No connection                                                                                                                                                                         |

| 6   | ANODE                    | Input LED anode                                                                                                                                                                       |

| 7   | ANODE                    | Input LED anode                                                                                                                                                                       |

| 8   | CATHODE                  | Input LED Cathode                                                                                                                                                                     |

| 9   | V <sub>S</sub>           | Common (IGBT emitter or MOSFET                                                                                                                                                        |

|     |                          | source) output supply voltage                                                                                                                                                         |

| 10  | V <sub>OUTN</sub>        | Driver output to turn off IGBT or MOSFET gate                                                                                                                                         |

| 11  | V <sub>OUTP</sub> /CLAMP | Driver output to turn on IGBT or MOSFET gate/miller clamp                                                                                                                             |

| 12  | $V_{DD2}$                | Positive output power supply                                                                                                                                                          |

| 13  | SS                       | Soft shutdown                                                                                                                                                                         |

| 14  | ос                       | Overcurrent input pin. When the voltage on the OC pin exceeds an internal reference voltage of 9V while the IGBT/ MOSFET is on, FAULT output is changed from logic high to low state. |

| 15  | (LED <sub>2</sub> )NC    | No connection                                                                                                                                                                         |

| 16  | V <sub>SS2</sub>         | Negative output power supply                                                                                                                                                          |

## **Ordering Information**

| Part Number | Option (RoHS Compliant) | Package | Surface Mount | Tape and Reel | IEC/EN/DIN EN<br>60747-5-5 | Quantity     |

|-------------|-------------------------|---------|---------------|---------------|----------------------------|--------------|

| ACPL-355JC  | -000E                   | SO-16   | Х             |               | Х                          | 45 per tube  |

|             | -500E                   |         | Х             | Х             | X                          | 850 per reel |

To order, choose a part number from the part number column and combine with the desired option from the option column to form an order entry.

#### Example 1:

ACPL-355JC-500E to order product of SO-16 Surface Mount package in Tape and Reel packaging with IEC/EN/DIN EN 60747-5-5 Safety Approval in RoHS compliant.

Option data sheets are available. Contact your Broadcom sales representative or authorized distributor for information.

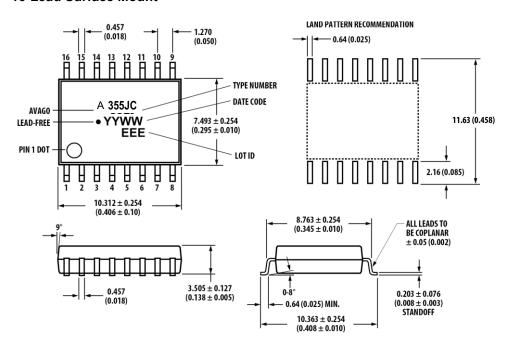

## **Package Outline Drawing**

#### 16-Lead Surface Mount

Dimensions are in inches (millimeters).

Floating lead protrusion is 0.25 mm (10 mils) maximum.

## **Recommended PB-Free IR Profile**

Recommended reflow condition as per JEDEC Standard, J-STD-020 (latest revision). Non-halide flux should be used.

## **Approvals**

The ACPL-355JC is approved by the following organizations.

| UL/cUL        | UL/cUL 1577, compliance with U.S. and Canadian requirements, component recognition program up to |

|---------------|--------------------------------------------------------------------------------------------------|

|               | $V_{ISO} = 5000 V_{RMS}$ .                                                                       |

| IEC/EN/DIN EN | IEC 60747-5-5                                                                                    |

| 60747-5-5     | EN 60747-5-5                                                                                     |

|               | DIN EN 60747-5-5                                                                                 |

### IEC/EN/DIN EN60747-5-5 Insulation Characteristics

| Description                                                                                                                                                                 | Symbol                | Characteristic <sup>a</sup> | Unit              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------|-------------------|

| Insulation Classification per DIN VDE 0110/1.89, Table 1                                                                                                                    |                       |                             |                   |

| For Rated Mains Voltage ≤ 600Vrms                                                                                                                                           |                       | I - IV                      |                   |

| For Rated Mains Voltage ≤ 1000Vrms                                                                                                                                          |                       | I - IV                      |                   |

| Climatic Classification                                                                                                                                                     |                       | 40/110/21                   |                   |

| Pollution Degree (DIN VDE 0110/1.89)                                                                                                                                        |                       | 2                           |                   |

| Maximum Working Insulation Voltage                                                                                                                                          | V <sub>IORM</sub>     | 2262                        | $V_{PEAK}$        |

| Input to Output Test Voltage, Method $b^b$<br>V <sub>IORM</sub> × 1.875 = V <sub>PR</sub> , 100% Production Test with $t_m$ = 1 seconds, partial discharge < 5 pC           | V <sub>PR</sub>       | 4242                        | V <sub>PEAK</sub> |

| Input to Output Test Voltage, Method a <sup>b</sup> V <sub>IORM</sub> × 1.6 = V <sub>PR</sub> , Type and Sample Test, t <sub>m</sub> = 10 seconds, partial discharge < 5 pC | V <sub>PR</sub>       | 3619                        | $V_{PEAK}$        |

| Highest Allowable Overvoltage (Transient Overvoltage t <sub>ini</sub> = 60 seconds)                                                                                         | V <sub>IOTM</sub>     | 8000                        | V <sub>PEAK</sub> |

| Safety-limiting Values – Maximum Values Allowed in the Event of a Failure                                                                                                   |                       |                             |                   |

| Case Temperature                                                                                                                                                            | T <sub>S</sub>        | 175                         | °C                |

| Input Power                                                                                                                                                                 | P <sub>S,INPUT</sub>  | 400                         | mW                |

| Output Power                                                                                                                                                                | P <sub>S,OUTPUT</sub> | 1200                        | mW                |

| Insulation Resistance at T <sub>S</sub> , V <sub>IO</sub> = 500V                                                                                                            | R <sub>S</sub>        | > 10 <sup>9</sup>           | Ω                 |

a. Isolation characteristics are guaranteed only within the safety maximum ratings which must be ensured by protective circuits in application. Surface mount classification is class A in accordance with CECCO0802.

b. Refer to IEC/EN/DIN EN 60747-5-5 Optoisolator Safety Standard section of the Broadcom Regulatory Guide to Isolation Circuits, AV02-2041EN, for a detailed description of Method a and Method b partial discharge test profiles.

# **Insulation and Safety Related Specifications**

| Parameter                                         | Symbol | Value | Units | Conditions                                                                                                                         |

|---------------------------------------------------|--------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------|

| Minimum External Air Gap (Clearance)              | L(101) | 8.3   | mm    | Measured from input terminals to output terminals, shortest distance through air.                                                  |

| Minimum External Tracking (Creepage)              | L(102) | 8.3   | mm    | Measured from input terminals to output terminals, shortest distance path along body.                                              |

| Minimum Internal Plastic Gap (Internal Clearance) |        | 0.5   | mm    | Through insulation distance conductor to conductor, usually the straight line distance thickness between the emitter and detector. |

| Tracking Resistance (Comparative Tracking Index)  | CTI    | > 600 | V     | DIN IEC 112/VDE 0303 Part 1                                                                                                        |

| Isolation Group                                   |        | I     |       | Material Group (DIN VDE 0110)                                                                                                      |

NOTE: All Broadcom data sheets report the creepage and clearance inherent to the optocoupler component itself. These dimensions are needed as a starting point for the equipment designer when determining the circuit insulation requirements. However, when mounted on a printed circuit board, minimum creepage and clearance requirements must be met as specified for individual equipment standards. For creepage, the shortest distance path along the surface of a printed circuit board between the solder fillets of the input and output leads must be considered (the recommended land pattern does not necessarily meet the minimum creepage of the device). Recommended techniques, such as grooves and ribs, may be used on a printed circuit board to achieve desired creepage and clearances. Creepage and clearance distances also change depending on factors such as pollution degree and insulation level.

# **Absolute Maximum Ratings**

| Parameter                                                 | Symbol                                 | Min.                   | Max.                   | Units | Note |

|-----------------------------------------------------------|----------------------------------------|------------------------|------------------------|-------|------|

| Storage Temperature                                       | T <sub>S</sub>                         | <b>–</b> 55            | 125                    | °C    |      |

| Operating Temperature                                     | T <sub>A</sub>                         | -40                    | 110                    | °C    |      |

| Output IC Junction Temperature                            | T <sub>J</sub>                         | _                      | 125                    | °C    |      |

| Average Input Current                                     | I <sub>F(AVG)</sub>                    | _                      | 25                     | mA    | а    |

| Peak Transient Input Current (< 1-µs pulse width, 300pps) | I <sub>F(TRAN)</sub>                   | _                      | 1.0                    | Α     |      |

| Reverse Input Voltage                                     | V <sub>R</sub>                         | _                      | 5                      | V     |      |

| Peak Output Current                                       | I <sub>O(PEAK)</sub>                   | _                      | 10                     | Α     | b    |

| Positive Input Supply Voltage                             | V <sub>DD1</sub>                       | 0                      | 7                      | V     |      |

| FAULT Output Current                                      | I <sub>FAULT</sub>                     | _                      | 10                     | mA    |      |

| FAULT Pin Voltage                                         | V <sub>FAULT</sub>                     | -0.5                   | V <sub>DD1</sub>       | V     |      |

| Total Output Supply Voltage                               | (V <sub>DD2</sub> - V <sub>SS2</sub> ) | -0.5                   | 35                     | V     |      |

| Negative Output Supply Voltage                            | (V <sub>S</sub> - V <sub>SS2</sub> )   | -0.5                   | 17                     | V     |      |

| Positive Output Supply Voltage                            | $(V_{DD2} - V_S)$                      | -0.5                   | $35 - (V_S - V_{SS2})$ | V     |      |

| Input Current (Rise/Fall Time)                            | $t_{r(IN)}/t_{f(IN)}$                  | _                      | 500                    | ns    |      |

| High Side Pull Up Voltage                                 | V <sub>OUTP</sub>                      | V <sub>SS2</sub> – 0.5 | V <sub>DD2</sub> + 0.5 | V     |      |

| Low Side Pull Down Voltage                                | V <sub>OUTN</sub>                      | V <sub>SS2</sub> – 0.5 | V <sub>DD2</sub> + 0.5 | V     |      |

| Overcurrent Pin Voltage                                   | V <sub>oc</sub>                        | V <sub>S</sub> – 0.5   | V <sub>DD2</sub> + 0.5 | V     |      |

| Peak Clamp Sinking Current                                | I <sub>CLAMP</sub>                     | _                      | 4                      | Α     |      |

| Miller Clamp Pin Voltage                                  | V <sub>CLAMP</sub>                     | V <sub>SS2</sub> – 0.5 | V <sub>DD2</sub> + 0.5 | V     |      |

| Output IC Power Dissipation                               | P <sub>O</sub>                         | _                      | 600                    | mW    | С    |

| Input LED Power Dissipation                               | P <sub>I</sub>                         | _                      | 110                    | mW    | d    |

- a. Derate linearly above 70°C free-air temperature at a rate of 0.3 mA/°C.

- b. Maximum pulse width = 1 μs, maximum duty cycle=1%. The output must be limited to –10.0A/10.0A of peak current by external resistors and connected to a total load bigger than 2 nF during application or board testing. See the Supply and Ground Planes Layout and Loading Conditions section to prevent output noise at 10A rated current.

- c. Derate linearly above 95°C free-air temperature at a rate of 20 mW/°C.

- d. Derate linearly above 95°C free-air temperature at a rate of 3.7 mW/°C. The maximum LED junction temperature should not exceed 125°C.

## **Recommended Operating Conditions**

| Parameter                      | Symbol                                 | Min. | Max.                   | Units | Note |

|--------------------------------|----------------------------------------|------|------------------------|-------|------|

| Operating Temperature          | T <sub>A</sub>                         | -40  | 110                    | °C    |      |

| Positive Input Supply Voltage  | V <sub>DD1</sub>                       | 4.5  | 5.5                    | V     |      |

| Total Output Supply Voltage    | (V <sub>DD2</sub> - V <sub>SS2</sub> ) | 15   | 30                     | V     |      |

| Negative Output Supply Voltage | (V <sub>S</sub> - V <sub>SS2</sub> )   | 0    | 15                     | V     |      |

| Positive Output Supply Voltage | $(V_{DD2} - V_S)$                      | 15   | $30 - (V_S - V_{SS2})$ | V     |      |

| Input Current (ON)             | I <sub>F(ON)</sub>                     | 7    | 11                     | mA    |      |

| Input Voltage (OFF)            | V <sub>F(OFF)</sub>                    | -3.6 | 0.5                    | V     |      |

# **Electrical Specifications (DC)**

All typical values at  $T_A = 25^{\circ}C$ ,  $V_{DD1} = 5V$ ,  $V_{DD2} - V_S = 15 V$ ,  $V_S - V_{SS2} = 15V$ ; all minimum and maximum specifications are at recommended operating conditions, unless otherwise noted.

| Parameter                                            | Symbol                    | Min.                    | Тур.                    | Max.                    | Units | Test Conditions                                                  | Figure | Note |

|------------------------------------------------------|---------------------------|-------------------------|-------------------------|-------------------------|-------|------------------------------------------------------------------|--------|------|

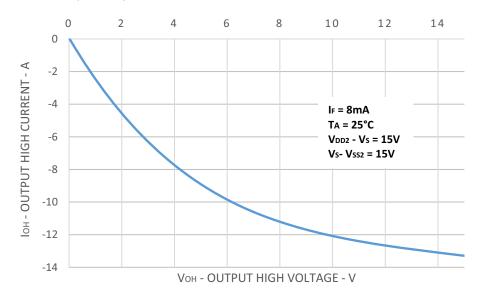

| V <sub>OUTP</sub> High Level Peak<br>Output Current  | I <sub>OH</sub>           | -7.5                    | -13                     | _                       | Α     | $V_{DD2} - V_{OUTP} = 15V$                                       | 3      | а    |

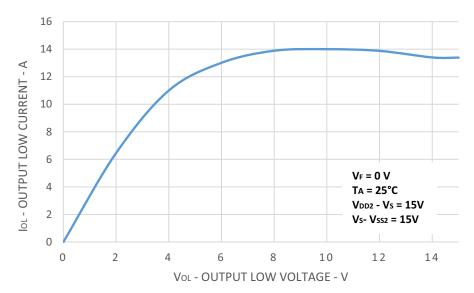

| V <sub>OUTN</sub> Low Level Peak<br>Output Current   | I <sub>OL</sub>           | 7.5                     | 14                      | _                       | Α     | $V_{OUTN} - V_{SS2} = 15V$                                       | 4      | а    |

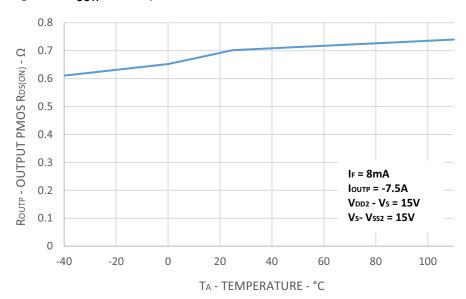

| V <sub>OUTP</sub> Output PMOS<br>R <sub>DS(ON)</sub> | R <sub>OUTP</sub>         | 0.4                     | 0.7                     | 1.5                     | Ω     | $I_{OP} = -7.5A$ , $I_F = 8 \text{ mA}$                          | 5      | а    |

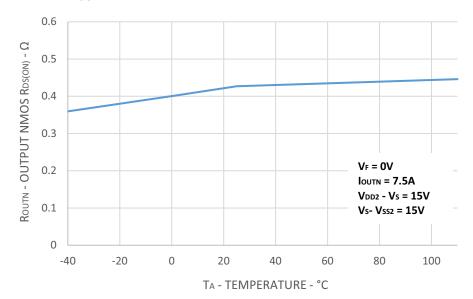

| V <sub>OUTN</sub> Output NMOS<br>R <sub>DS(ON)</sub> | R <sub>OUTN</sub>         | 0.3                     | 0.4                     | 1.2                     | Ω     | I <sub>ON</sub> = 7.5A, V <sub>F</sub> = 0V                      | 6      | а    |

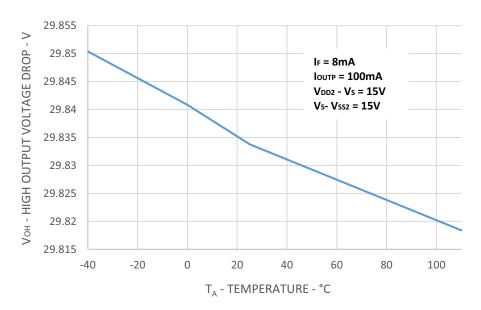

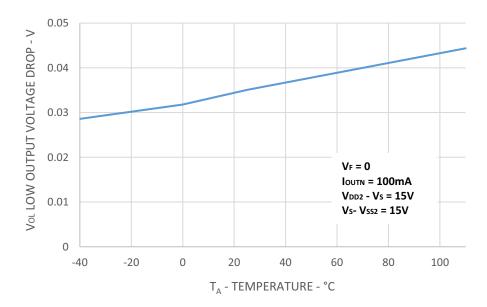

| V <sub>OUTP</sub> Output Voltage                     | V <sub>OH</sub>           | V <sub>DD2</sub> - 0.60 | V <sub>DD2</sub> – 0.15 | _                       | V     | $I_{OP} = -100 \text{ mA}, I_F = 8 \text{ mA}$                   | 1      | b, c |

| V <sub>OUTN</sub> Output Voltage                     | V <sub>OL</sub>           | _                       | V <sub>SS2</sub> + 0.04 | V <sub>SS2</sub> + 0.60 | V     | I <sub>ON</sub> = 100 mA, V <sub>F</sub> = 0V                    | 2      |      |

| Clamp Threshold Voltage                              | V <sub>TH_CLAMP</sub>     | _                       | V <sub>SS2</sub> + 2    | V <sub>SS2</sub> + 2.2  | V     |                                                                  |        |      |

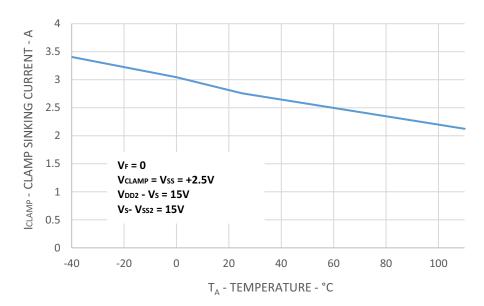

| Clamp Low Level Sinking<br>Current                   | I <sub>CLAMP</sub>        | 1.7                     | 2.75                    | _                       | Α     | $V_{CLAMP} = V_{SS2} + 2.5V$                                     | 7      |      |

| Clamp Low Level Peak<br>Sinking Current              | I <sub>CLAMPPK</sub>      | 2.5A                    | 4.6                     | _                       | Α     | V <sub>CLAMP</sub> = V <sub>SS2</sub> + 10V                      |        |      |

| Clamp Output Transistor R <sub>DS(ON)</sub>          | R <sub>DS,CLAMP</sub>     | _                       | 1.1                     | 2                       | Ω     | I <sub>CLAMP</sub> = 2.5A                                        |        |      |

| SS Pull Down Current                                 | I <sub>OSS</sub>          | 0.5                     | 1                       | _                       | Α     | SS – V <sub>SS2</sub> < 15V,<br>I <sub>F</sub> = 8 mA, OC = Open |        |      |

| SS R <sub>DSON</sub>                                 | R <sub>OUTSS</sub>        | _                       | 1.35                    | _                       | Ω     | I <sub>SS</sub> = 0.5A, I <sub>F</sub> = 8mA,<br>OC = Open       |        |      |

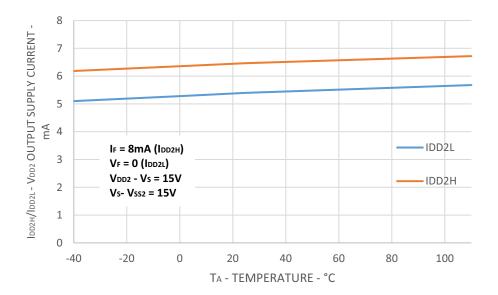

| High Level Output Supply Current (V <sub>DD2</sub> ) | I <sub>DD2H</sub>         | _                       | 6.5                     | 8                       | mA    | I <sub>F</sub> = 8 mA, No Load                                   | 8      |      |

| Low Level Output Supply Current (V <sub>DD2</sub> )  | I <sub>DD2L</sub>         | _                       | 5.4                     | 7                       | mA    | V <sub>F</sub> = 0V, No Load                                     | 8      |      |

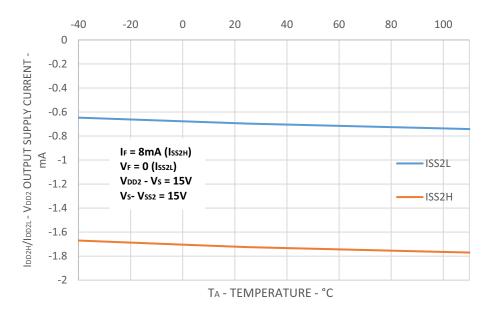

| High Level Output Supply Current(V <sub>SS2</sub> )  | I <sub>SS2H</sub>         | -2.2                    | -1.7                    | _                       | mA    | I <sub>F</sub> = 8 mA, No Load                                   | 9      |      |

| Low Level Output Supply Current (V <sub>SS2</sub> )  | I <sub>SS2L</sub>         | -1                      | -0.7                    | _                       | mA    | V <sub>F</sub> = 0V, No Load                                     | 9      |      |

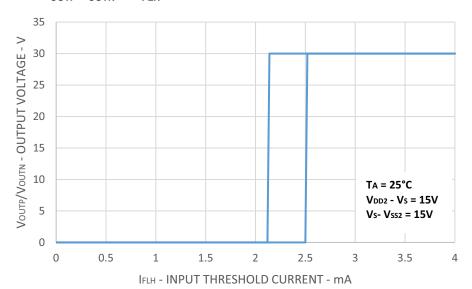

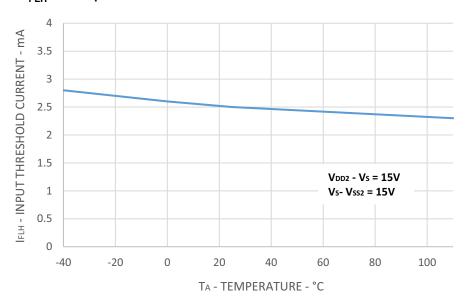

| Input Threshold Current<br>Low to High               | I <sub>FLH</sub>          | 0.2                     | 2.5                     | 6.5                     | mA    |                                                                  | 10, 11 |      |

| Input Threshold Voltage<br>High to Low               | V <sub>FHL</sub>          | 0.8                     | _                       | _                       | ٧     |                                                                  |        |      |

| Input Forward Voltage                                | V <sub>F</sub>            | 1.2                     | 1.4                     | 1.95                    | V     | I <sub>F</sub> = 8 mA                                            |        |      |

| Temperature Coefficient of Input Forward Voltage     | $\Delta V_F / \Delta T_A$ |                         | -1.7                    | _                       | mV/°C | I <sub>F</sub> = 8 mA                                            |        |      |

| Input Reverse Breakdown<br>Voltage                   | BV <sub>R</sub>           | 5                       | _                       | _                       | V     | Ι <sub>R</sub> = 100 μΑ                                          |        |      |

| Input Capacitance                                    | C <sub>IN</sub>           | _                       | 23                      | _                       | pF    | $f = 1 MHz, V_F = 0V$                                            |        |      |

| Parameter                                                                                  | Symbol                                     | Min. | Тур. | Max. | Units | Test Conditions                                   | Figure | Note    |

|--------------------------------------------------------------------------------------------|--------------------------------------------|------|------|------|-------|---------------------------------------------------|--------|---------|

| UVLO Threshold,<br>V <sub>DD2</sub> – V <sub>S</sub>                                       | V <sub>UVLO+</sub>                         | 12.2 | 13.2 | 13.8 | V     | $I_F = 8 \text{ mA},$<br>$V_{OUTP} - V_E > 5V$    |        | b, c, d |

|                                                                                            | V <sub>UVLO-</sub>                         | 11.2 | 12.1 | 12.7 | V     | $I_F = 8 \text{ mA},$<br>$V_{OUTP} - V_E < 5V$    |        | b, c, e |

| UVLO Hysteresis,<br>V <sub>DD2</sub> – V <sub>S</sub>                                      | V <sub>UVLO+</sub> –<br>V <sub>UVLO-</sub> | 0.5  | 1    | _    | V     |                                                   |        |         |

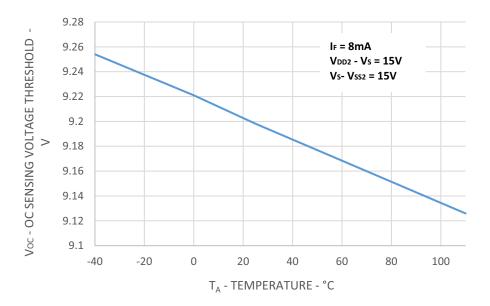

| OC Sensing Voltage<br>Threshold with Reference<br>to V <sub>S</sub>                        | V <sub>OC</sub>                            | 8.5  | 9.2  | 9.8  | V     | $V_{DD2} - V_S > V_{UVLO+}$                       | 12     | С       |

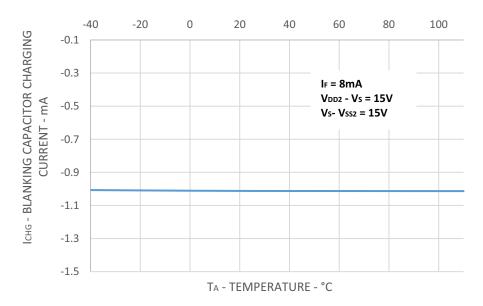

| Blanking Capacitor<br>Charging Current                                                     | I <sub>CHG</sub>                           | 0.95 | 1    | 1.05 | mA    | V <sub>OC</sub> = 2V                              | 13     | c, f    |

| OC Low Voltage when<br>Blanking Capacitor<br>Discharge with Reference<br>to V <sub>S</sub> | V <sub>DSCHG</sub>                         | _    | 1.4  | 2.3  | V     | I <sub>DSCHG</sub> = 50 mA                        |        | c, f    |

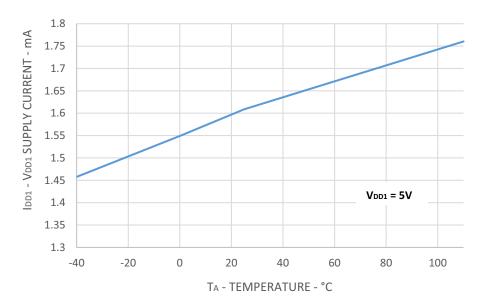

| Input Supply Current (V <sub>DD1</sub> )                                                   | I <sub>DD1</sub>                           | _    | 1.6  | 2.5  | mA    |                                                   | 14     |         |

| V <sub>CC1</sub> Under Voltage Turn<br>On Threshold                                        | V <sub>UV1_TH+</sub>                       |      | 4.5  | _    | V     |                                                   |        |         |

| V <sub>CC1</sub> Under Voltage Turn<br>Off Threshold                                       | V <sub>UV1_TH-</sub>                       | _    | 3.8  | _    | V     |                                                   |        |         |

| FAULT Logic Low Output<br>Current                                                          | I <sub>FAULTL</sub>                        | 4    | 8.5  | _    | mA    | V <sub>FAULT</sub> = 0.4 V, V <sub>DD1</sub> = 5V |        |         |

| FAULT Logic High Output Current                                                            | I <sub>FAULTH</sub>                        | _    | _    | 20   | μA    | V <sub>FAULT</sub> = V <sub>DD1</sub> = 5V        |        |         |

| UVLO Logic Low Output<br>Current                                                           | I <sub>UVLOL</sub>                         | 4    | 8.5  | _    | mA    | V <sub>UVLO</sub> = 0.4 V, V <sub>DD1</sub> = 5V  |        |         |

| UVLO Logic High Output<br>Current                                                          | I <sub>UVLOH</sub>                         |      | _    | 20   | μA    | $V_{\text{UVLO}} = V_{\text{DD1}} = 5V$           |        |         |

- a. Output is sourced at -10A/10A with a maximum pulse width =  $10 \mu s$ .

- b. 15V is the recommended minimum operating positive supply voltage (V<sub>DD2</sub> V<sub>S</sub>) to ensure adequate margin in excess of the maximum V<sub>UVLO+</sub> threshold of 13.8V. For High Level Output Voltage testing, V<sub>OUTP</sub> is measured with a 50-µs pulse load current. When driving capacitive loads, V<sub>OUTP</sub> will approach V<sub>DD2</sub> as I<sub>OUTP</sub> approaches zero units.

- c. When the system is out of UVLO (V<sub>DD2</sub> V<sub>S</sub> > VUVLO+), the OC detection feature of the ACPL-355JC will be the primary source of IGBT/ MOSFET protection. UVLO must be unlocked to ensure OC is functional. When V<sub>DD2</sub> exceeds the V<sub>UVLO+</sub> threshold, OC will remain functional until V<sub>DD2</sub> is below the V<sub>UVLO-</sub> threshold. The OC detection and UVLO features of the ACPL-355JC work together to ensure constant IGBT/MOSFET protection.

- d. This is the "increasing" (that is, turn-on or "positive going" direction) of  $V_{DD2} V_S$ .

- e. This is the "decreasing" (that is, turn-off or "negative going" direction) of  $\rm V_{DD2} \rm V_{S}.$

- f. See the OC Fault Detection Blanking Time section for further details

# **Switching Specifications (AC)**

All typical values at  $T_A = 25$ °C,  $V_{DD1} = 5$ V,  $V_{DD2} - V_S = 15$ V,  $V_S - V_{SS2} = 15$ V; all minimum and maximum specifications are at recommended operating conditions, unless otherwise noted.

| Parameter                                                     | Symbol                                        | Min.            | Тур. | Max. | Units | Test Conditions                                                                                                                                  | Fig.          | Note |

|---------------------------------------------------------------|-----------------------------------------------|-----------------|------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|

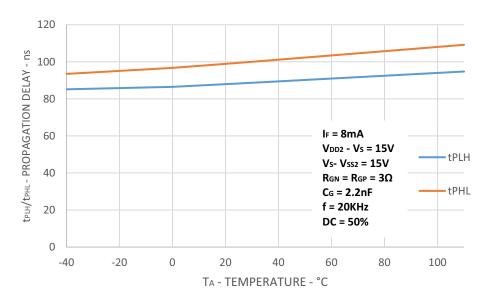

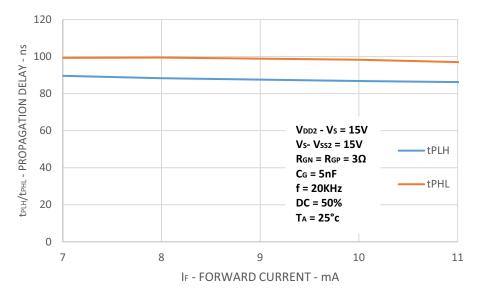

| Propagation Delay Time to High V <sub>OUTP</sub> Output Level | t <sub>PLH</sub>                              | 40              | 90   | 140  | ns    | $R_{GP} = 3\Omega$ , $R_{GN} = 3\Omega$ ,<br>$C_{G} = 2.2$ nF, $f = 20$ kHz,                                                                     | 15, 16,<br>21 | а    |

| Propagation Delay Time to Low V <sub>OUTN</sub> Output Level  | t <sub>PHL</sub>                              | 40              | 100  | 140  | ns    | Duty Cycle = 50%, I <sub>F</sub> = 8 mA                                                                                                          | 15, 16,<br>21 | b    |

| Pulse Width Distortion                                        | PWD                                           | -50             | 10   | 50   | ns    |                                                                                                                                                  |               | С    |

| Propagation Delay Difference<br>Between Any Two Parts         | PDD<br>(t <sub>PLH</sub> – t <sub>PHL</sub> ) | <del>-7</del> 0 | _    | 70   | ns    |                                                                                                                                                  |               | d    |

| Propagation Delay Skew                                        | t <sub>PSK</sub>                              | _               | _    | 60   | ns    |                                                                                                                                                  |               | е    |

| 10% to 90% Rise Time on V <sub>OUTP</sub>                     | t <sub>R</sub>                                | _               | 35   | _    | ns    | $R_{GP} = 3\Omega$ , $R_{GN} = 3\Omega$ ,                                                                                                        |               |      |

| 90% to 10% Fall Time on V <sub>OUTN</sub>                     | t <sub>F</sub>                                | _               | 33   | _    | ns    | $C_G = 2.2 \text{ nF, f} = 20 \text{ kHz,}$<br>Duty Cycle = 50%, $I_F = 8\text{mA}$                                                              |               |      |

| OC Blanking Time                                              | t <sub>OC(BLANKING)</sub>                     | _               | 0.6  | 1    | μs    | $R_{GP} = 3\Omega$ , $R_{GN} = 3\Omega$ ,                                                                                                        | 20            | f    |

| OC Detection to 90% V <sub>GATE</sub> Delay                   | t <sub>OC(90%)</sub>                          | 0.05            | 0.13 | 0.3  | μs    | $C_G = 2.2 \text{ nF, f} = 2.5 \text{kHz,}$<br>- Duty Cycle = 50%, $I_F = 8 \text{ mA,}$                                                         | 20            | g    |

| OC Detection to V <sub>GATE</sub> = 2V Delay                  | t <sub>OC(2V)</sub>                           | 0.1             | 0.2  | 0.5  | μs    | $R_{SS} = 15\Omega, C_F = 330 \text{ pF},$                                                                                                       | 20            | h    |

| OC Detection to OC Pull Low<br>Propagation Delay              | t <sub>OC(LOW)</sub>                          | _               | 0.3  | _    | μs    | $R_F = 10 \text{ k}\Omega$                                                                                                                       | 20            | į    |

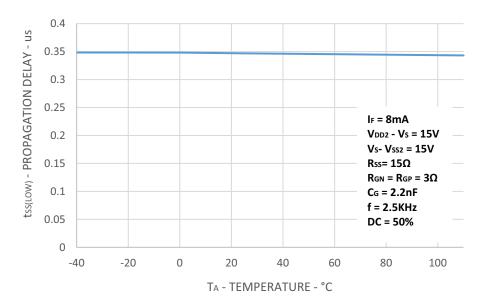

| OC Detection to SS Pull Low<br>Propagation Delay              | t <sub>SS(LOW)</sub>                          | _               | 0.35 | 0.8  | μs    |                                                                                                                                                  | 17, 20        | j    |

| OC Detection to Low Level FAULT Signal Delay                  | t <sub>OC(FAULT)</sub>                        | _               | 1.7  | 5    | μs    |                                                                                                                                                  | 20            | k    |

| Output Mute Time due to<br>Overcurrent                        | t <sub>OC(MUTE)</sub>                         | 0.13            | 0.2  | 0.4  | ms    |                                                                                                                                                  | 18, 20        | I    |

| Time Input Kept Low Before Fault Reset to High                | t <sub>OC(RESET)</sub>                        | 0.13            | 0.2  | 0.4  | ms    | $C_F = 330 \text{ pF, } R_F = 10 \text{ k}\Omega$                                                                                                | 18, 20        | m    |

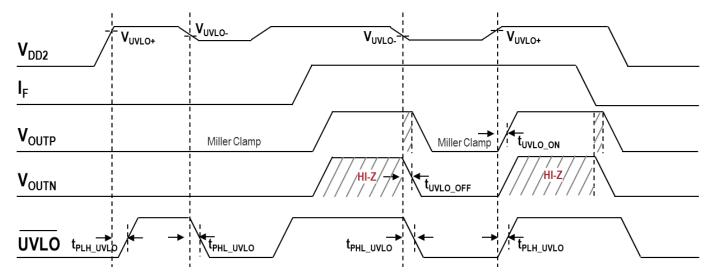

| V <sub>DD2</sub> to UVLO High Delay                           | t <sub>PLH_UVLO</sub>                         | _               | 17   | 25   | μs    | $C_U = 330 \text{ pF}, R_U = 10 \text{ k}\Omega$                                                                                                 | 22            | n    |

| V <sub>DD2</sub> to UVLO Low Delay                            | t <sub>PHL_UVLO</sub>                         | _               | 14   | 30   | μs    | $C_U = 330 \text{ pF}, R_U = 10 \text{ k}\Omega$                                                                                                 | 22            | 0    |

| V <sub>DD2</sub> UVLO to VOUTP High Delay                     | t <sub>UVLO_ON</sub>                          | _               | 4    | _    | μs    |                                                                                                                                                  | 22            | р    |

| V <sub>DD2</sub> UVLO to VOUTN Low Delay                      | t <sub>UVLO_OFF</sub>                         | _               | 3.5  | _    | μs    |                                                                                                                                                  | 22            | q    |

| Output High Level Common Mode Transient Immunity              | CM <sub>H</sub>                               | 100             | _    | _    | kV/µs | $T_A = 25^{\circ}\text{C}, V_{CM} = 1500\text{V}, \\ V_{DD1} = 5\text{V}, C_F = 330 \text{ pF}, \\ R_F = 10 \text{ k}\Omega, I_F = 8 \text{ mA}$ |               | r, s |

| Output Low Level Common Mode<br>Transient Immunity            | CM <sub>L</sub>                               | 100             | _    | _    | kV/µs | $T_A = 25^{\circ}\text{C}, V_{CM} = 1500\text{V}, \\ V_{DD1} = 5\text{V}, C_F = 330 \text{ pF}, \\ R_F = 10 \text{ k}\Omega, V_F = 0\text{V}$    |               | s, t |

- a.  $t_{PLH}$  is defined as propagation delay from 50% of LED input  $I_F$ , to 50% of  $V_{OUTP}$  high level output.

- b.  $t_{PHL}$  is defined as propagation delay from 50% of LED input  $I_F$ , to 50% of  $V_{OUTN}$  low level output.

- c. Pulse Width Distortion (PWD) is defined as |t<sub>PHL</sub> t<sub>PLH</sub>| for any given unit.

- d. Propagation Delay Difference (PDD) is the difference between tPHL and tPLH between any two units under the same test condition.

- e. Propagation Delay Skew (t<sub>PSK</sub>) is the difference in t<sub>PHL</sub> or t<sub>PLH</sub> between any two units under the same test condition.

- f. The internal delay time to respond to an OC fault condition without any external blanking capacitor.

ACPL-355JC-DS102 Broadcom

- g. The amount of time from when OC threshold is exceeded to 90% of  $V_{GATE}$  at mentioned test conditions.

- h. The amount of time from when OC threshold is exceeded to V<sub>GATE</sub> at 2V at mentioned test conditions.

- i. The amount of time from when OC threshold is exceeded to 10% of OC low voltage.

- j. The amount of time from when OC threshold is exceeded to 10% of SS (Soft Shut) low voltage.

- k. The amount of time from when OC threshold is exceeded to FAULT output low.

- I. The amount of time when OC threshold is exceeded, output is muted to LED input.

- m. The amount of time when OC mute time is expired, LED input must be kept low for FAULT status to return to High.

- n. The delay time when V<sub>DD2</sub> exceeds UVLO+ threshold to UVLO high 50% of UVLO positive-going edge.

- The delay time when V<sub>DD2</sub> exceeds UVLO- threshold to UVLO low 50% of UVLO negative-going edge.

- p. The delay time when  $V_{DD2}$  exceeds UVLO+ threshold to 50% of  $V_{OUTP}$  high level output.

- q. The delay time when  $V_{DD2}$  exceeds UVLO- threshold to 50% of  $V_{OUTN}$  low level output.

- r. Common mode transient immunity in the high state is the maximum tolerable  $dV_{CM}/dt$  of the common mode pulse,  $V_{CM}$ , to assure that the output will remain in the high state (that is,  $V_{DD2} V_{OUTP} < 1.0V$  or FAULT > 2V).  $V_{DD2}$  must be higher than  $V_{UVLO+}$ .

- s. Split resistor network in the ratio 3:1 with  $324\Omega$  at the anode and  $107\Omega$  at the cathode.

- t. Common mode transient immunity in the low state is the maximum tolerable  $dV_{CM}/dt$  of the common mode pulse,  $V_{CM}$ , to assure that the output will remain in a low state (that is,  $V_{OUTN} V_{SS2} < 1.0V$  or FAULT > 2V).  $V_{DD2}$  must be higher than  $V_{UVLO+}$ .

# **Package Characteristics**

| Parameter                                | Symbol           | Min. | Тур.  | Max. | Units            | Test Conditions                                  | Note    |

|------------------------------------------|------------------|------|-------|------|------------------|--------------------------------------------------|---------|

| Input-Output Momentary Withstand Voltage | V <sub>ISO</sub> | 5000 |       |      | V <sub>RMS</sub> | RH < 50%, t = 1 minute,<br>T <sub>A</sub> = 25°C | a, b, c |

| Resistance (Input-Output)                | R <sub>I-O</sub> |      | 109   |      | Ω                | V <sub>I-O</sub> = 500 V <sub>DC</sub>           | С       |

| Capacitance (Input-Output)               | C <sub>I-O</sub> |      | 1.3   |      | pF               | f = 1 MHz                                        |         |

| Thermal coefficient between:             |                  |      |       |      | °C/W             |                                                  | d       |

| Input IC due to heating of Input IC      | R <sub>11</sub>  |      | 42.53 |      |                  |                                                  |         |

| Input IC due to heating of LED1          | R <sub>12</sub>  |      | 17.10 |      |                  |                                                  |         |

| Input IC due to heating of Output IC     | R <sub>13</sub>  |      | 13.01 |      |                  |                                                  |         |

| Input IC due to heating of LED2          | R <sub>14</sub>  |      | 33.06 |      |                  |                                                  |         |

| Input LED1 due to heating of Input IC    | R <sub>21</sub>  |      | 10.91 |      |                  |                                                  |         |

| Input LED1 due to heating of LED1        | R <sub>22</sub>  |      | 88.49 |      |                  |                                                  |         |

| Input LED1 due to heating of Output IC   | R <sub>23</sub>  |      | 17.08 |      |                  |                                                  |         |

| Input LED1 due to heating of LED2        | R <sub>24</sub>  |      | 20.75 |      |                  |                                                  |         |

| Output IC due to heating of Input IC     | R <sub>31</sub>  |      | 13.62 |      |                  |                                                  |         |

| Output IC due to heating of LED1         | R <sub>32</sub>  |      | 29.74 |      |                  |                                                  |         |

| Output IC due to heating of Output IC    | R <sub>33</sub>  |      | 33.90 |      |                  |                                                  |         |

| Output IC due to heating of LED2         | R <sub>34</sub>  |      | 28.67 |      |                  |                                                  |         |

| Input LED2 due to heating of Input IC    | R <sub>41</sub>  |      | 17.56 |      |                  |                                                  |         |

| Input LED2 due to heating of LED1        | R <sub>42</sub>  |      | 19.09 |      |                  |                                                  |         |

| Input LED2 due to heating of Output IC   | R <sub>43</sub>  |      | 16.51 |      |                  |                                                  |         |

| Input LED2 due to heating of LED2        | R <sub>44</sub>  |      | 84.90 |      |                  |                                                  |         |

a. In accordance with UL/cUL1577, each optocoupler is proof tested by applying an insulation test voltage ≥ 9000 V<sub>RMS</sub> for 1 second. This test

is performed before the 100% production test for partial discharge (method b) shown in IEC/EN/DIN EN 60747-5-5 Insulation Characteristic

Table, if applicable.

- c. The device considered a two-terminal device: Pins 1 to 8 are shorted together, and pins 9 to 16 are shorted together.

- d. The device was mounted on a high conductivity test board as per JEDEC 51-7. For further details, see the Thermal Calculation section.

b. The Input-Output Momentary Withstand Voltage is a dielectric voltage rating that should not be interpreted as an input-output continuous voltage rating. For the continuous voltage rating, refer to your equipment level safety specification or IEC/EN/DIN EN 60747-5-5 Insulation Characteristics Table

Figure 1: V<sub>OH</sub> vs. Temperature

Figure 2: V<sub>OL</sub> vs. Temperature

Figure 3: I<sub>OH</sub> vs. V<sub>OH</sub>

Figure 4: I<sub>OL</sub> vs. V<sub>OL</sub>

Figure 5:  $R_{OUTP}$  vs. Temperature

Figure 6:  $R_{OUTN}$  vs. Temperature

Figure 7:  $I_{CLAMP}$  vs. Temperature

Figure 8:  $I_{DD2L}/I_{DD2H}$  vs. Temperature

Figure 9:  $I_{SS2L}/I_{SS2H}$  vs. Temperature

Figure 10: V<sub>OUTP</sub>/V<sub>OUTN</sub> vs. I<sub>FLH</sub>

Figure 11:  $I_{FLH}$  vs. Temperature

Figure 12:  $V_{OC}$  vs. Temperature

Figure 13:  $I_{CHG}$  vs. Temperature

Figure 14: I<sub>DD1</sub> vs. Temperature

Figure 15:  $t_{PLH}/t_{PHL}$  vs. Temperature

Figure 16: t<sub>PLH</sub>/t<sub>PHL</sub> vs. I<sub>F</sub>

Figure 17: t<sub>SS(LOW)</sub> vs. Temperature

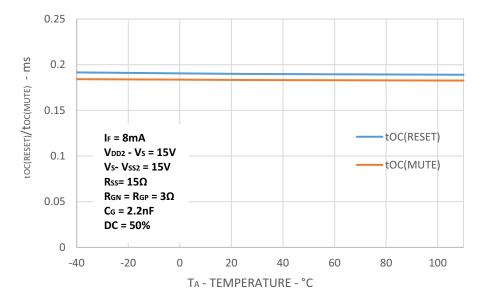

Figure 18:  $t_{OC(RESET)}/t_{OC(MUTE)}$  vs. Temperature

## **Applications Information**

#### **Recommended Application Circuit**

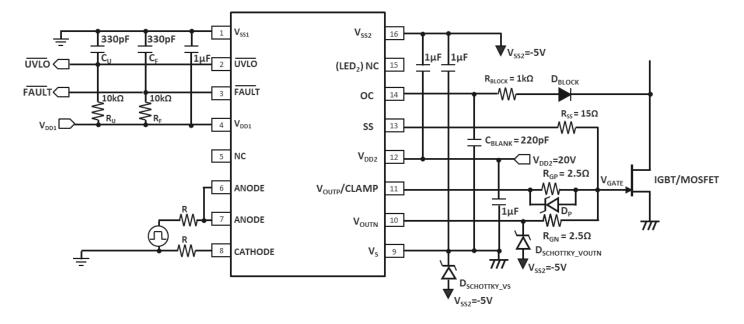

Figure 19: Recommended Application Circuit for ACPL-355JC

The ACPL-355JC has an LED input control input and two fault reporting mechanisms: namely  $V_{DD2}$  under voltage lockout (UVLO) and IGBT/MOSFET overcurrent (FAULT). These open drain FAULT and UVLO GFAULT outputs are connected to 10-k $\Omega$  pull-up resistors and 330-pF filtering capacitors and are suitable for wired OR applications. UVLO has the highest fault priority and follows by FAULT. The supplies ( $V_{DD1}$  and  $V_{DD2}$ ) are connected to four 1- $\mu$ F bypass decoupling capacitors to provide the large transient currents necessary during a switching transition.

The two resistors (R) connected to input LED's anode and cathode are recommended to be split in the ratio of 3:1. They balance the common mode impedances at the LED's anode and cathode, which helps to equalize the common mode voltage changes at the anode and cathode to give high CMR performance.

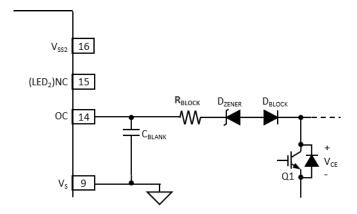

The HV blocking diode,  $D_{BLOCK}$ ,  $R_{BLOCK}$ , and 220-pF blanking capacitor protect the OC pin and prevent false fault detection. During overcurrent fault condition, the IGBT/MOSFET is soft shutdown through the SS pin, and the rate of shut down can be adjusted by  $R_{SS}$ .

The gate resistor ( $R_{GP}$  and  $R_{GN}$ ) limits gate current and indirectly controls the IGBT/MOSFET switching times. Schottky diode,  $D_P$ , is used together with the CLAMP function to shunt parasitic IGBT/MOSFET Miller current during the off cycle.

Schottky diodes,  $D_{SCHOTTKY\_VOUTN}$  and  $D_{SCHOTTKY\_VS}$ , prevent  $V_{OUT}$  and  $V_{S}$  from going below  $V_{SS2}$  due to negative transient caused by parasitic inductance.

### **Output Control**

The secondary output stage ( $V_{OUT}$ , CLAMP, OC, and SS) is controlled by the combination of  $V_{DD2}$ , LED current ( $I_F$ ) and overcurrent (OC) conditions. Note that  $V_{DD1}$  provides the power supply to the device's fault reporting mechanisms. The secondary output stage ( $V_{OUT}$ , CLAMP, OC, and SS) remains operational when there is no  $V_{DD1}$  supply. The following table shows the logic truth table for these outputs. The logic level is defined by the respective threshold of each function pin.

|                       | Inputs    |                |               | 5                 | Secondary Output         | Fault Reporting Outputs |      |       |

|-----------------------|-----------|----------------|---------------|-------------------|--------------------------|-------------------------|------|-------|

| Condition             | $V_{DD2}$ | I <sub>F</sub> | ос            | V <sub>OUTN</sub> | V <sub>OUTP</sub> /CLAMP | SS                      | UVLO | FAULT |

| V <sub>DD2</sub> UVLO | Low       | Х              | Not Active    | Low               | Low(CLAMP)               | High-Z                  | Low  | High  |

| Overcurrent           | High      | Low            | Not Active    | Low               | Low(CLAMP)               | High-Z                  | High | High  |

|                       | High      | High           | Active(OC)    | High-Z            | Low(CLAMP)               | Low                     | High | Low   |

| Normal                | High      | Low            | Not Active    | Low               | Low(CLAMP)               | High-Z                  | High | High  |

| Switching             | High      | High           | Active(no OC) | High-Z            | High(VOUTP)              | High-Z                  | High | High  |

#### Introduction to Overcurrent (or DESAT) Detection and Protection

The power stage of a typical three-phase inverter is susceptible to several types of failures, most of which are potentially destructive to the power IGBT/MOSFET. These failure modes can be grouped into four basic categories: phase and/or rail supply short circuits due to user misconnect or bad wiring, control signal failures due to noise or computational errors, overload conditions induced by the load, and component failures in the gate drive circuitry. Under any of these fault conditions, the current through the IGBT/MOSFET can increase rapidly, causing excessive power dissipation and heating. The IGBT/MOSFET becomes damaged when the current load approaches the saturation current of the device, and the collector/drain to emitter/source voltage rises above the saturation voltage level. The drastically increased power dissipation very quickly overheats the power device and destroys it. To prevent damage to the drive, fault protection must be implemented to reduce or turn-off the IGBT/MOSFET during a fault condition.

The ACPL-355JC OC pin monitors the drain/source voltages of the MOSFET or the collector/emitter voltages of the IGBT. When the MOSFET goes into overcurrent or IGBT into desaturation, these voltages exceed the predetermined threshold,  $V_{OC}$ . The ACPL-355JC triggers a local fault shutdown sequence and slowly reduces the high overcurrent to prevent damaging the voltage spikes. The fault is reported to controller through the isolated feedback channel of the ACPL-355JC. During the off state (no LED input) of the IGBT, the fault detect circuitry is disabled to prevent false "fault" signals.

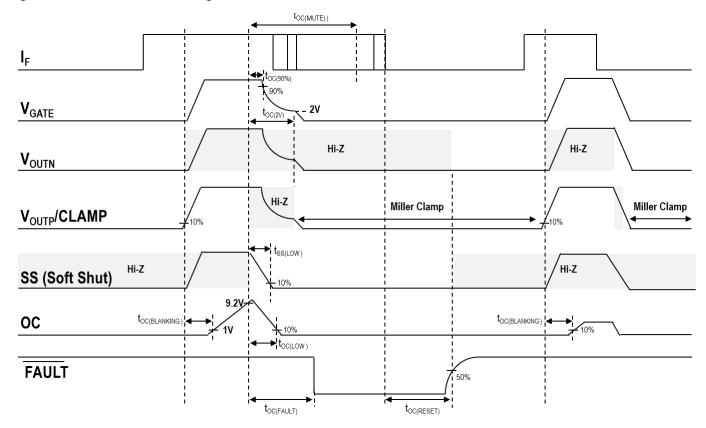

## **Description of Operation during Overcurrent Condition**

- 1. The OC terminal monitors IGBT's  $V_{CE}$  or MOSFET  $V_{DS}$  voltage.

- When the voltage on the OC terminal exceeds 9.2V, the output voltages (V<sub>OUTP</sub> and V<sub>OUTN</sub>) go to Hi-Z state, and the SS pulls down the V<sub>GATE</sub> at a slow rate adjustable using resistor R<sub>SS</sub>.

- 3. FAULT output goes low, notifying the microcontroller of the fault condition.

- 4. The mcrocontroller takes appropriate action.

- When t<sub>OC(MUTES)</sub> expires, LED input must be kept low for t<sub>OC(RESET)</sub> before fault condition is cleared. FAULT status

returns to high and SS output returns to the Hi-Z state.

- 6. In the event LED goes high during t<sub>OC(RESET)</sub>, the t<sub>OC(RESET)</sub> timing is reset, and the LED input must be kept low for another t<sub>OC(RESET)</sub> before the fault condition is cleared.

- 7. V<sub>GATE</sub> starts to respond to the LED input after the fault condition is cleared.

Figure 20: Circuit Behaviors during Overcurrent Event

## **OC Fault Detection Blanking Time**

The OC fault detection circuitry must remain disabled for a short time period following the turn-on of the IGBT to allow the collector voltage to fall below the OC threshold. This time period, called the total OC blanking time, is controlled by the both internal OC blanking time t<sub>OC(BLANKING)</sub> (Figure 20) and external blanking time, determined by internal charge current, the OC voltage threshold, and the external blanking capacitor.

The total blanking time is calculated in terms of internal blanking time ( $t_{OC(BLANKING)}$ ), external capacitance ( $C_{BLANK}$ ), FAULT threshold voltage ( $V_{OC}$ ), and blanking capacitor charge current ( $I_{CHG}$ ) as the following:

$t_{BLANK} = t_{OC(BLANKING)} + C_{BLANK} \times V_{OC} / I_{CHG}$

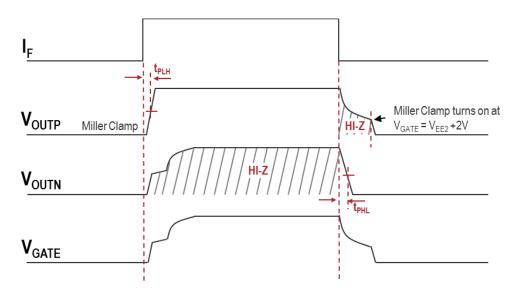

## **Description of Gate Driver and Miller Clamping**

The gate driver is directly controlled by the LED current. When LED current is driven high, the output of the ACPL-355JC is capable of delivering 10A maximum sourcing current to drive the IGBT's/MOSFET's gate. While the LED is switched off, the gate driver can provide 10A maximum sinking current to switch the gate off fast. Additionally, the miller clamping pull-down transistor is activated when output voltage reaches about 2V with respect to V<sub>SS2</sub> to provide low impedance path to miller current as shown in Figure 21.

Figure 21: Gate Drive Signal Behavior

## **Description of Under Voltage Lockout**

Insufficient gate voltage to IGBT/MOSFET can increase the turn-on resistance of IGBT/MOSFET, resulting a large power loss and IGBT/MOSFET damage due to high heat dissipation. The ACPL-355JC monitors the output power supply,  $V_{DD2}$ , constantly. When output power supply is lower than the under voltage lockout (UVLO), the threshold gate driver output shuts off to protect IGBT/MOSFET from low voltage bias. During power-up, the UVLO feature locks the gate driver output low to prevent unwanted turn on at lower supply voltage.

Figure 22: Circuit Behaviors at Power-Up and Power-Down

### Selecting the Gate Resistor (Rg)

**Step 1**: Calculate  $R_G$  minimum from the  $I_{O(PEAK)}$  specification. The IGBT/MOSFET and  $R_G$  in Figure 19 can be analyzed as a simple RC circuit with a voltage supplied by ACPL-355JC.

$$\begin{split} R_G &\geq \frac{V_{DD2} - V_{SS2}}{I_{OPEAK}} - R_{OUTP(MIN)} \\ &= \frac{20 - (-5)V}{10\,A} - 0.4\,\Omega \qquad \qquad \text{or} \\ &= \frac{20 - (-5)V}{10\,A} - 0.3\,\Omega \\ &= 2.1\,\Omega \qquad \qquad = 2.2\,\Omega \end{split}$$

The external gate resistor,  $R_G$ , and internal minimum turn-on resistance, RDSON, ensure the output current will not exceed the device absolute maximum rating of 10A. In this case, we will use worst case  $R_G \ge 2.5\Omega$ .

**Step 2:** Check the ACPL-355JC power dissipation and increase  $R_G$  if necessary. The ACPL-355JC total power dissipation  $(P_T)$  is equal to the sum of the LED1 power  $(P_{E1})$ , input IC power  $(P_I)$ , output IC power  $(P_O)$ , and LED2 power  $(P_{E2})$ .

$$P_T = P_{E1} + P_I + P_O + P_{E2}$$

Assuming operation conditions of  $I_F$  = 8 mA,  $R_G$  = 2.5 $\Omega$ , Max Duty Cycle = 80%,  $Q_G$  = 0.2  $\mu$ C, f = 150 kHz, and  $T_A$  = 85°C.

#### **Calculation of LED1 Power Dissipation**

$$P_{E1} = I_F \times V_F \times Duty Cycle$$

= 8 mA × 1.95V × 0.8 = 12.5 mW

#### **Calculation of Input IC Power Dissipation**

$$P_I = I_{DD1} (Max) \times V_{DD}1$$

(Recommended Max)

= 2.5 mA × 5.5V = 13.75 mW

#### **Calculation of Onput IC Power Dissipation**

$$\begin{split} P_{O} &= P_{O(BIAS)} + P_{O(SWITCHING)} \\ &= I_{DD2} \times (V_{DD2} - V_{SS2}) + P_{HS} + P_{LS} \\ P_{HS} &= (V_{DD2} \times Q_{G} \times f) * R_{OUTP(MAX)} / (R_{OUTP(MAX)} + R_{G}) / 2 \\ P_{LS} &= (V_{DD2} \times Q_{G} \times f) \times R_{OUTN(MAX)} / (R_{OUTN(MAX)} + R_{G}) / 2 \\ P_{HS} &= (25V \times 0.2 \ \mu\text{C} \times 150 \ \text{kHz}) \times 1.5\Omega / (1.5\Omega + 2.5\Omega) / 2 = 140.63 \ \text{mW} \\ P_{LS} &= (25V \times 0.2 \ \mu\text{C} \times 150 \ \text{kHz}) \times 1.2\Omega / (1.2\Omega + 2.5\Omega) / 2 = 121.62 \ \text{mW} \\ P_{O} &= 8 \ \text{mA} \times 25V + 140.63 \ \text{mW} + 121.62 \ \text{mW} \\ &= 462.2 \ \text{mW} < 600 \ \text{mW} \ (P_{O(MAX)} \ @ 95^{\circ}\text{C}) \end{split}$$

The value of 8 mA for I<sub>DD2</sub> in the previous equation is the maximum I<sub>CC2</sub> over the entire operating temperature range.

Because  $P_O$  is less than  $P_{O(MAX)}$ ,  $Rg = 2.5\Omega$  is correct for the power dissipation.

#### **Calculation of LED2 Power Dissipation**

```

P_{E2} = I_F \times V_F \times Duty Cycle

= 8 mA × 1.95V × 0.1 = 1.56 mW

```

LED2 is designed to be driven by the output IC at 8-mA LED current at 10% duty cycle.

#### **Thermal Calculation**

Application and environmental designs for the ACPL-355JC must ensure that the junction temperature of the internal ICs and LED within the gate driver optocoupler do not exceed 125°C. The equations that follow are for the purposes of calculating the maximum power dissipation effect on junction temperatures.

```

LED1 Junction Temperature, T<sub>F1</sub>

= R_{21} \times P_{E1} + R_{22} \times P_1 + R_{23} \times P_0 + R_{24} \times P_{E2} + T_A

= 10.91°C/W × 12.5 mW + 88.49°C/W × 13.75 mW + 17.08°C/W × 462.2 mW + 20.75°C/W × 1.56 mW + 85°C

= 94.3°C

Input IC Junction Temperature, T<sub>I</sub>

= R_{11} \times P_{F1} + R_{12} \times P_{I} + R_{13} \times P_{O} + R_{14} \times P_{F2} + T_{A}

= 42.53°C/W *12.5mW + 17.1°C/W *13.75mW + 13.01°C/W *462.2mW + 33.06°C/W *1.56mW + 85°C

= 91.8°C

Output IC Junction Temperature, To

= R_{31} \times P_{F1} + R_{32} \times P_{I} + R_{33} \times P_{O} + R_{34} \times P_{F2} + T_{A}

= 13.62°C/W × 12.5 mW + 29.74°C/W × 13.75 mW + 33.9°C/W × 462.2 mW + 28.67°C/W × 1.56 mW + 85°C

= 101.3°C

LED2 Junction Temperature, T<sub>F2</sub>

= R_{41} \times P_{E1} + R_{42} \times P_{I} + R_{43} \times P_{O} + R_{44} \times P_{E2} + T_{A}

= 17.56°C/W × 12.5 mW + 19.09°C/W × 13.75 mW + 16.51°C/W × 462.2 mW + 84.9°C/W × 1.56 mW + 85°C

= 93.2°C

```

## OC (Overcurrent) Blocking Diodes and Threshold

The  $D_{BLOCK}$  diode's function is to conduct forward current, allowing sensing of the IGBT's  $V_{CE}$  or MOSFET's  $V_{DS}$  when it is "on" and to block high voltages when it is "off".

During IGBT/MOSFET switching off and towards the end of the forward conduction of the  $D_{BLOCK}$  diode, a reverse current flows for short time. This reverse recovery effect causes the diode to not be able to achieve its blocking capability until the mobile charge in the junction is depleted. During this time, there is commonly a very high dV/dt voltage ramp rate across the IGBT/MOSFET. This results in  $I_{CHARGE} = C_{D-BLOCK} \times dV/dt$  charging current, which charges the blanking capacitor,  $C_{BLANK}$ . To minimize this charging current and avoid false overcurrent triggering, it is best to use fast response diodes.

In the application circuit shown in Figure 23, the voltage on pin 14 (OC) is  $V_{OC} = (I_{CHG} \times R_{BLOCK}) + V_F + V_{CE}$ , (where  $V_F$  is the forward ON voltage of  $D_{BLOCK}$  and  $V_{CE}$  is for example, the IGBT collector-to-emitter voltage). The value of  $V_{OC,FAULT(TH)}$ , which triggers OC to signal a FAULT condition, is nominally  $9V - (I_{CHG} \times R_{BLOCK}) - V_F$ . If desired, this threshold voltage can be decreased by using multiple  $D_{BLOCK}$  diodes or low voltage zener diode in series. If n is the number of  $D_{BLOCK}$  diodes, the nominal threshold value becomes  $V_{OC,FAULT(TH)} = 9.2V - (I_{CHG} \times R_{BLOCK}) - (n \times V_F)$ . If a Zener diode is used, the nominal threshold value becomes  $V_{OC,FAULT(TH)} = 9.2V - (I_{CHG} \times R_{BLOCK}) - V_F - V_Z$ . In the case of using two diodes instead of one, diodes with half of the total required maximum reverse-voltage rating may be chosen.

Figure 23: OC (Overcurrent) Blocking Diodes and Threshold

#### **OC Pin Protection Resistor**

The freewheeling of flyback diodes connected across the IGBT/MOSFET can have large instantaneous forward voltage transients that greatly exceed the nominal forward voltage of the diode. This situation may result in a large negative voltage spike on the OC pin, which draws substantial current out of the driver if protection is not used. To limit this current to levels that do not damage the driver IC, insert a 1-k $\Omega$  resistor in series with the D<sub>BLOCK</sub> diode.

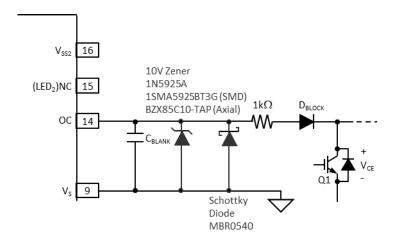

## **False Fault Prevention Diodes**

One of the situations that may cause the driver to generate a false fault signal is if the substrate diode of the driver becomes forward biased. This situation can occur if the reverse recovery spikes coming from the IGBT/MOSFET freewheeling diodes bring the OC pin below ground. Hence, the OC pin voltage is "brought" above the threshold voltage. These negative-going voltage spikes are typically generated by inductive loads or reverse recovery spikes of the IGBT/MOSFETs' free-wheeling diodes. To prevent a false fault signal, connect a Zener diode and Schottky diode across the OC pin and  $V_S$  pin

This circuit solution is shown in Figure 24. The Schottky diode prevents the substrate diode of the gate driver optocoupler from being forward-biased while the Zener diode (value around 10V) prevents any positive high-transient voltage to affect the OC pin.

Figure 24: False Fault Prevention Diodes

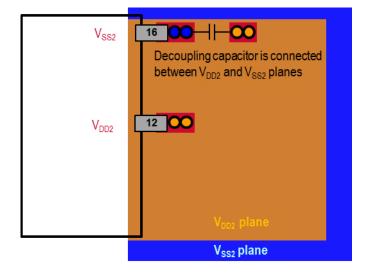

# **Supply and Ground Planes Layout and Loading Conditions**

At 10A rated high current switching, the decoupling capacitor must be close to the  $V_{DD}$  and  $V_{SS}$  pins. And due to the fast switching, large  $V_{DD}$  and  $V_{SS}$  planes should prevent noise by lowering the parasitic inductance. Without the  $V_{DD}$  and  $V_{SS}$  planes, connect the total load bigger than 2 nF during all applications or board testing to prevent output noise.

Figure 25: Recommended V<sub>DD2</sub> and V<sub>SS2</sub>, Supply and Ground Planes Layout

| Copyright © 2021-2023 Broadcom. All Rights Reserved. The term "Broadcom" refers to Broadcom Inc. and/or its                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| subsidiaries. For more information, go to www.broadcom.com. All trademarks, trade names, service marks, and logos referenced herein belong to their respective companies.                                                                                                                                                                                                                                                                                                                        |

| Broadcom reserves the right to make changes without further notice to any products or data herein to improve reliability, function, or design. Information furnished by Broadcom is believed to be accurate and reliable. However, Broadcom does not assume any liability arising out of the application or use of this information, nor the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>№ BROADCOM</b> °                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

**Broadcom Limited:**

ACPL-355JC-000E ACPL-355JC-500E